ไอซี CS8416 (Digital Audio Interface Receiver)

เป็นไอซีที่ใช้ถอดรหัสสัญญาณเสียงดิจิตอลที่มีคุณสมบัติภายในตัวสูง

สามารถรับสัญญาณเสียงขนาด16-24 บิทที่มีความถี่ในการสุ่มในช่วง 32kHz –

192kHz โดยสัญญาณที่ส่งเข้ามาถอดรหัสในไอซีจะเป็นรูปแบบ S/PDIF

ที่ส่งออกมาจากเครื่องเล่น CD หรือ DVD สามารถถอดรหัสแยกสัญญาณข้อมูล

(Data) และสัญญาณนาฬิกา (Clock)

ที่ส่งออกมาแบบมัลติเพลกซ์ในสายส่งเส้นเดียว

ซึ่งสัญญาณนาฬิกาที่ได้จากการถอดรหัสออกมานั้นจะมีสัญญาณรบกวนในระดับต่ำ

ไอซี CS8416 สามารถเลือกโหมดการทำงานได้ 2 โหมด คือ ซอฟต์แวร์โหมด และ

ฮาร์ดแวร์โหมด ซึ่งการควบคุมก็จะแตกต่างกันออกไป

โดยต่อไปนี้จะอธิบายถึงการทำงานของไอซี CS8416 ในฮาร์ดแวร์โหมด

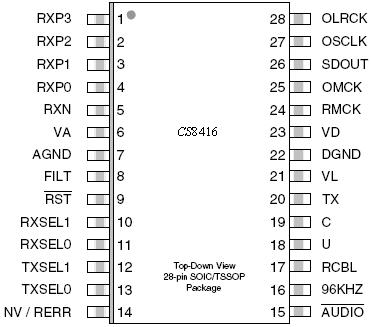

รูป1 ตำแหน่งขาของไอซี CS8416 ในฮาร์ดแวร์โหมด

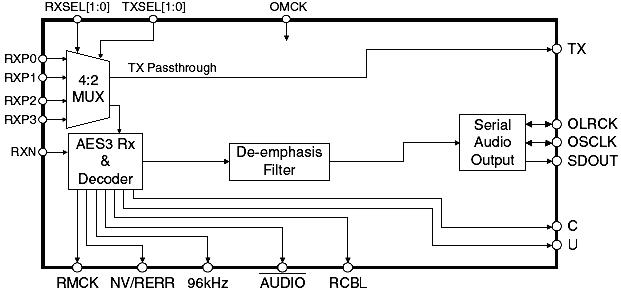

รูป 2 บล็อกไดอะแกรมภายในไอซี CS8416 ในฮาร์ดแวร์โหมด

อธิบายหน้าที่ของแต่ละขาและการต่อใช้งานในฮาร์ดแวร์โหมดของไอซี CS8416 ในแต่ละส่วนตารางที่ 1 ขาสัญญาณ CS8416 ในโหมด ฮาร์ดแวร์ (HW)

ส่วนภาคจ่ายไฟ

ขา

|

ชื่อขา

|

รายละเอียดขา

|

6

|

VA

(Analog Power Supply)

|

ขาไฟเลี้ยงบวกของ ภาคแอนะลอกโดยปกติใช้ 3.3 โวลต์ |

23

|

VD

(Digital Power Supply)

|

ขาไฟเลี้ยงบวกของ ภาคดิจิตอลโดยปกติใช้ 3.3 โวลต์ |

21

|

VL

(Logic Power Supply)

|

ไฟเลี้ยงบวกของ ภาคลอจิกโดยปกติใช้ 3.3 หรือ 5 โวลต์ |

7

|

AGND

(Analog Ground Supply)

|

ขากราวด์สำหรับวงจรภาคแอนะลอก |

22

|

DGND

(Digital Ground Supply)

|

ขากราวด์สำหรับวงจรภาคดิจิตอล |

8

|

FILT

(PLL Loop Filter)

|

เป็นขาที่ทำหน้าที่ล็อกสัญญาณอินพุต S/PDIF ที่เข้ามา โดยทำงานร่วมกับวงจรกรองความถี่ต่ำผ่านที่ต่ออยู่กับขานี้ |

9

|

RST

(Reset)

|

เป็นขาที่เอารีเซตการทำงานของ CS8416 |

ขา

|

ชื่อขา

|

รายละเอียดขา

|

27

|

OSCLK

(Serial Audio Output Bit Clock)

|

เป็นสัญญาณนาฬิกาขาออก ของระบบเสียงดิจิตอลซึ่งนำไปต่อกับขาสัญญาณนาฬิกาของไอซี DAC ซึ่งอยู่ในส่วนการแปลงดิจิตอลเป็นแอนะลอก |

28

|

OLRCK

(Serial Audio Output Left/Right Clock)

|

เป็นสัญญาณนาฬิกาขาออกที่ใช้สำหรับระบุข้อมูลจากขา SDOUT ว่าเป็นของสัญญาณด้านซ้าย หรือ สัญญาณด้านขวามีค่าเท่ากับ ความถี่แซมปลิ้ง ซึ่งนำไปต่อกับขา สัญญาณนาฬิกาซ้ายขวา ของไอซี DAC ซึ่งอยู่ในภาคแปลงดิจิตอลเป็นแอนะลอก |

26

|

SDOUT

(Serial Audio Output Data)

|

ขาสัญญาณของข้อมูลเสียงที่ถูกส่งออกมาในรูปแบบอนุกรม ซึ่งนำไปต่อกับขาข้อมูล ของไอซี DAC ซึ่งอยู่ในภาคแปลงดิจิตอลเป็นแอนะลอก |

24

|

RMCK

(Input Serial Recovered Master Clock)

|

เป็นขาเอาต์พุตของสัญญาณ นาฬิกาหลัก RMCK ที่ได้จากเฟสล็อกลูป ซึ่งสามารถเลือกความถี่ของสัญญาณนาฬิกาได้โดยการต่อ Pull Down ผ่านตัวต้านทาน 47kΩ กับ DGND ที่ขา U จะให้ความถี่สัญญาณนาฬิกาที่ 256*Fs และถ้าต่อ Pull up ผ่านตัวต้านทาน 47kΩ กับ VL ที่ขา U จะให้ความถี่สัญญาณนาฬิกาที่ 128* Fs |

25

|

OMCK

(System Clock)

|

เป็นขาที่ใช้ในการเลือกสัญญาณนาฬิกา OMCK ในระบบอัตโนมัติให้ออกที่ขา RMCK เมื่อเฟสล็อกลูปไม่ล็อกสัญญาณ |

ส่วนรับสัญญาณ SPDIF

ขา

|

ชื่อขา

|

รายละเอียดขา

|

5

|

RXN

(Negative S/PDIF Input)

|

เป็นกราวด์สำหรับสัญญาณอินพุตที่รับเข้ามา

|

4

|

RXP0

(SPDIF Input 0)

|

เป็นขารับสัญญาณ SPDIF จากแหล่งจ่ายสัญญาณ สามารถรับเข้ามาได้ 4 สัญญาณพร้อมกัน และจะถูกเลือกไปใช้งาน

|

3

|

RXP1

(SPDIF Input 1)

|

|

2

|

RXP2

(SPDIF Input 2 / SPDIF Input 6)

|

|

1

|

RXP3

(SPDIF Input 3 )

|

|

10

|

RXSEL1

(Receiver_MUX Selector)

|

เป็นขาที่ใช้เซตเลือกรับสัญญาณจากอินพุตRXP0- RXP3

|

11

|

RXSEL0

(Receiver_MUX Selector)

|

|

12

|

TXSEL1

(TX Pin MUX Selection)

|

เป็นขาที่ใช้เซตเลือกสัญญาณจากอินพุตส่งผ่านโดยตรงไปที่

ขา TX โดยไม่ผ่านการถอดรหัสเพื่อให้ขา TX

ทำหน้าที่เป็นแหล่งจ่ายสัญญาณดิจิตอล (TX source) ของไอซี CS8416

|

13

|

TXSEL0

(TX Pin MUX Selection)

|

ขา

|

โหมด

|

ชื่อขา

|

รายละเอียดขา

|

19

|

HW

|

C(Serial Audio Format Output Mode Select 0)

|

เป็นขาสำหรับการเลือกรูปแบบของสัญญาณเสียงดิจิตอลทางด้านเอาต์พุต |

20

|

HW

|

TX (SPDIF MUX Pass through)

|

เป็นขาที่ให้สัญญาณ SPDIF จากอินพุตที่ถูกเลือกโดยขา TXSEL มาออกยังขานี้ |

18

|

HW

|

U(RMCK Frequency Selector)

|

เป็นขาที่ใช้สำหรับการกำหนดค่าของตัวคูณความถี่ของสัญญาณ RMCK= 256xfs หรือ 128 x fs |

17

|

HW

|

RCBL(Serial Port Mode Selector)

|

เป็นขาที่เอาไว้สำหรับเลือกว่าตัว CS8416 นี้ทำงานในรูปแบบมาสเตอร์หรือว่าสเลฟโหมด |

16

|

HW

|

96kHz (Emphasis Audio Match Mode Selector)

|

เป็นขาที่เอาไว้สำหรับเลือกส่วนของดิจิตอลฟิลเตอร์ |

14

|

HW

|

NV/RERR (Non-Validity Receiver

Error/Receiver Error)

|

เป็นขาที่เอาไว้สำหรับเลือกโหมดการแจ้งรูปแบบความผิดพลาดในการทำงานของ CS8416 |

15

|

HW

|

AUDIO(Serial Audio Format Output Mode Select 1)

|

เป็นขาสำหรับการเลือกรูปแบบของสัญญาณเสียงดิจิตอลทางด้านเอาต์พุต |

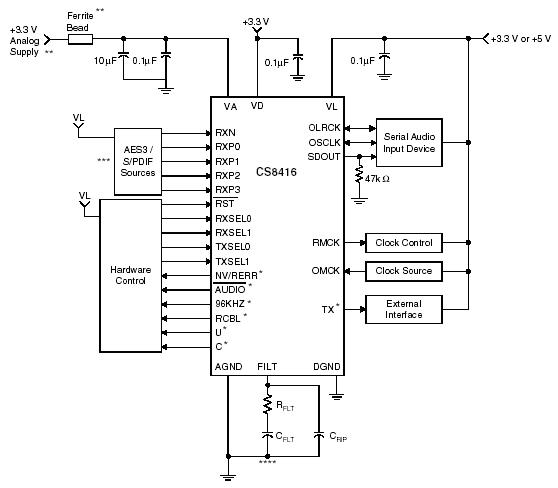

รูปแบบการต่อวงจร CS8416 ในแบบ ฮาร์ดแวร์โหมด

รูปที่ 3 แสดงรูปแบบการต่อวงจร CS8416

โดยพออธิบายการต่อใช้งานวงจร CS8416 อย่างย่อๆได้คือ

บล็อคAES3/SPDIF Source ส่วนที่รับสัญญาณอินพุตเข้ามาและส่งไป ที่ขา RXP[3:0] และขา RXN เป็นขาที่ใช้ในการรับสัญญาณ S/PDIF มาทำการถอดรหัสโดยจะใช้ส่วนที่ทำหน้าที่ควบคุมเพื่อรับสัญญาณอินพุตและรูป แบบของสัญญาณเอาท์พุตโดยที่ขา RXSEL0 และ RXSEL1 จะเป็นตัวที่ใช้กำหนดสัญญาณอินพุต

บล็อค Hardware Control เป็นส่วนภาคควบคุมใช้การควบคุมแบบ Hardware Mode โดยการต่อที่ขาควบคุมแบบ Pull up กับ VL หรือ Pull down กับ DGND เพื่อควบคุมไอซีให้ทำงานในแบบต่างๆ

บล็อก Serial Audio Input Device เป็นส่วนที่ส่งสัญญาณ Audioที่ถอดรหัสแล้วส่งออกไปที่ ไอซี DAC

บล็อก Clock Control ส่วนที่รับ Clock จากสัญญาณ Audioที่ถอดรหัสแล้วเพื่อนำ Clock นี้ไปใช้ประโยชน์ เช่นใช้ทำ Digital Filter

บล็อก Clock Source เป็นส่วนที่เลือกว่าจะใช้ Clock จาก Clock Control หรือไม่

บล็อก External Interface เป็นส่วนที่ส่งสัญญาณ SPDIF ที่ยังไม่ถอดรหัสหรือสัญญาณที่ไม่ใช้ SPDIF เช่นสัญญาณ DTS หรือ Dolby Digital ส่งผ่านจาก CS8416 ออกไปใช้งานที่ส่วนอื่นของวงจรต่อไป

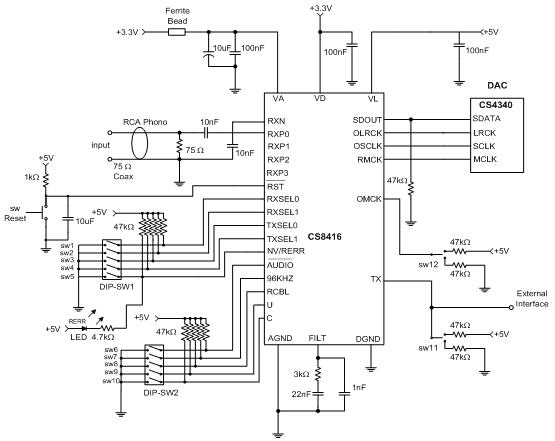

วงจรการต่อใช้งานของไอซี CS8416 ในฮาร์ดแวร์โหมด

รูปที่ 4 วงจรการต่อใช้งานของไอซี CS8416 ในฮาร์ดแวร์โหมด

ตารางที่ 2 การเลือกรับสัญญาณทางอินพุตในฮาร์ดแวร์โหมด

| RXSEL1 , RXSEL0 |

00

|

ให้ขา RXP0 รับสัญญาณจากอินพุต |

01

|

ให้ขา RXP1 รับสัญญาณจากอินพุต | |

10

|

ให้ขา RXP2 รับสัญญาณจากอินพุต | |

11

|

ให้ขา RXP3 รับสัญญาณจากอินพุต |

|

| TXSEL1 , TXSEL0 |

00

|

ให้ส่งผ่านสัญญาณที่ขา RXP0 ไปยังขา TX |

01

|

ให้ส่งผ่านสัญญาณที่ขา RXP1 ไปยังขา TX | |

10

|

ให้ส่งผ่านสัญญาณที่ขา RXP2 ไปยังขา TX | |

11

|

ให้ส่งผ่านสัญญาณที่ขา RXP3 ไปยังขา TX |

ตารางที่ 3 การกำหนดเอาต์พุตของไอซี CS8416 ให้ทำงานในลักษณะต่างๆ ในฮาร์ดแวร์โหมด

| Pin Name | Pull Down to DGND Function | Pull Up to VL Function |

| SDOUT | Hardware Mode | Software Mode |

| RCBL | Serial Port Slave Mode | Serial Port Master Mode |

| AUDIO | Serial Port Select 1 (SFSEL1) = 0 | Serial Port Select 1 (SFSEL1) = 1 |

| C | Serial Port Select 0 (SFSEL0) = 0 | Serial Port Select 0 (SFSEL0) = 1 |

| U | RMCK Frequency = 256*Fs | RMCK Frequency = 128*Fs |

| TX | Normal Phase Detector update rate | Higher phase Detector update rate |

| 96 kHz | Emphasis Audio Math Off | Emphasis Audio Math On |

| NV/RERR | NVERR Selected | RERR Selected |

- ขา SDOUT เป็นการกำหนดให้ไอซี CS8416 ทำงานในโหมดฮาร์ดแวร์หรือซอฟต์แวร์ โดยการเลือกเซตสวิตช์ที่ต่ออยู่กับขานี้ให้เป็นแบบ Pull Down สำหรับการทำงานในโหมดฮาร์ดแวร์ และเซตสวิตช์ให้เป็นแบบ Pull Up สำหรับการทำงานในโหมดซอฟต์แวร์

- ขา RCBL เป็นการกำหนดให้สัญญาณเสียงอนุกรมที่พอร์ตเอาต์พุตของไอซี CS8416 ได้แก่ขา OLRCK, OSCLK และ SDOUT เป็นมาสเตอร์โหมด หรือ สเลฟโหมด โดยถ้าเซตสวิตช์ที่ขานี้เป็นแบบ Pull Down จะทำงานในสเลฟโหมด ที่ขา OLRCK และ OSCLK จะเป็นอินพุตใช้สัญญาณนาฬิกา (Clock) จาก RMCK และถ้าเซตสวิตช์เป็นแบบ Pull Up จะทำงานในมาสเตอร์โหมด ที่ขา OLRCK และ OSCLK จะเป็นเอาต์พุตใช้สัญญาณนาฬิกาภายใน จาก OMCK

- ขา AUDIO และ C ใช้เลือกรูปแบบสัญญาณเสียงดิจิตอลว่าต้องการให้ไอซี CS8416 ถอดรหัสออกมาในรูปแบบใด โดยถ้าการเซตสวิตช์ที่ขานี้เป็นแบบ Pull Down จะมีค่าเป็น “0” และถ้าเซตสวิตช์เป็นแบบ Pull Up จะมีค่าเป็น “1” ซึ่งการเซตเพื่อเลือกรูปแบบของสัญญาณเสียงแสดงในตารางที่4

- ขา U เป็นขาที่ใช้เลือกความถี่ของสัญญาณนาฬิกา RMCK โดยถ้าเซตสวิตช์ที่ขานี้เป็นแบบ Pull Down จะกำหนดความถี่ของ RMCK เท่ากับ 256*Fs และถ้าเซตสวิตช์ให้เป็นแบบ Pull Up จะกำหนดความถี่ของ RMCK เท่ากับ 128*Fs

- ขา TX เป็นขาใช้เปลี่ยนแปลงตัวตรวจสอบเฟสเพื่อล็อกสัญญาณที่อินพุต โดยถ้าเซตสวิตช์ที่ขานี้เป็นแบบ Pull Down จะให้มีการเปลี่ยนแปลงตัวตรวจสอบเฟส (Phase- Detector) ในอัตราปกติทำให้สัญญาณนาฬิกา RMCK มี Wideband jitter ในระดับต่ำแต่จะเพิ่ม in-band jitter และถ้าเซตสวิตช์ที่ขานี้เป็นแบบ Pull Up จะให้มีเปลี่ยนแปลงตัวตรวจสอบเฟสในอัตราที่สูงขึ้น ทำให้สัญญาณนาฬิกา RMCK มี In-Band Jitter ในระดับต่ำ แต่จะเพิ่ม Wideband Jitter

- ขา 96kHz เป็นขาเอาต์พุตให้ทำหน้าที่ในการตรวจสอบว่าถ้าค่าความถี่สุ่มของสัญญาณ อินพุตน้อยกว่าหรือเท่ากับ 48 kHz เอาต์พุตที่ขานี้จะมีค่าเป็น “0” และถ้าค่าความถี่สุ่มของสัญญาณอินพุตมากกว่าหรือเท่ากับ 88 kHz เอาต์พุตที่ขานี้จะมีค่าเป็น “1” แต่ถ้าค่าความถี่สุ่มของสัญญาณอินพุตไม่อยู่ในช่วงนี้ เอาต์พุตที่ขานี้บอกไม่ได้ว่าเป็นค่าใด โดยสามารถเลือกเซตสวิตช์ที่ขานี้ได้ด้วยการต่อแบบ Pull Down ถ้าไม่ต้องการให้มีการตรวจสอบ และถ้าเซตสวิตช์ให้เป็นแบบ Pull Up จะมีการตรวจสอบดังกล่าว

- ขา NV/RERR เป็นขาที่ใช้แสดงข้อผิดพลาดในการรับสัญญาณเข้ามาถอดรหัส ซึ่งสามารถเลือกได้ว่าจะแสดงความผิดพลาดจากอะไร โดยการเลือกเซตสวิตช์ที่ขานี้เป็นแบบ Pull Down คือการเลือกแสดงความผิดพลาดแบบ NVRERR และถ้าเลือกเซตสวิตช์เป็นแบบ Pull Up คือการเลือกแสดงความผิดพลาดแบบ RERR

Ø NVRERR คือการแสดงความผิดพลาดของสัญญาณเหมือนกับ RERR แต่ว่าไม่ได้ตรวจสอบที่บิต V(validity) เท่านั้น

ตารางที่ 4 การเซตค่าเลือกรูปแบบข้อมูลสัญญาณเสียงดิจิตอลแบบอนุกรม (Audio Serial Data) ที่เอาต์พุตในฮาร์แวร์โหมด

Pin name

|

AUDIO/C

|

Format select

|

00

|

Left Justified 24 bit | |

AUDIO,C

|

01

|

I2S 24 bit |

10

|

Right Justified 24 bit | |

11

|

Direct AES3 |

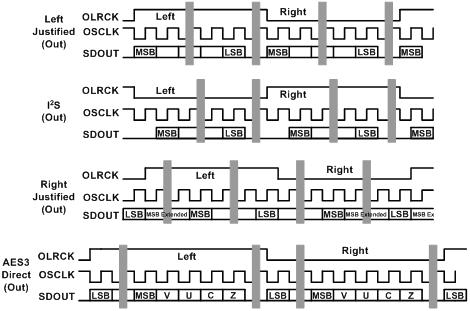

รูปที่ 5 รูปแบบสัญญาณเสียงที่เอาต์พุตของไอซี CS8416

จากรูปที่5 เป็นรูปแบบข้อมูลสัญญาณเสียงดิจิตอลแบบอนุกรมของ CS8416 สามารถถอดรหัสออกมาได้ทั้ง 4 รูปแบบได้แก่¨ Left Justified จะมีรูปแบบของสัญญาณเสียงอนุกรม SDOUT สัมพันธ์กับสัญญาณ OLRCK คือ บิตนัยสำคัญสูงสุด(MSB) ของ SDOUT จะอยู่ชิดทางด้านซ้ายของสัญญาณ OLRCK

¨ I2S จะมีรูปแบบของสัญญาณเสียงอนุกรม SDOUT สัมพันธ์กับสัญญาณ OLRCK คือสัญญาณ SDOUT จะอยู่ตรงกึ่งกลางของสัญญาณ OLRCK

¨ Right Justified จะมีรูปแบบของสัญญาณเสียงอนุกรม SDOUT สัมพันธ์กับสัญญาณ OLRCK คือ บิตนัยสำคัญสูงสุด(MSB) ของ SDOUT จะอยู่ชิดทางด้านขวาของสัญญาณ OLRCK

¨ Direct AES3 จะมีรูปแบบของสัญญาณเสียงอนุกรม SDOUT สัมพันธ์กับสัญญาณ OLRCK คือ บิตนัยสำคัญน้อยสุด(LSB) ของ SDOUT จะอยู่ชิดทางด้านซ้ายของสัญญาณ OLRCK

จากรูปแบบของสัญญาณเสียงที่ถูกถอดรหัสออกมา จะพบว่ามีรูปแบบไม่เหมือนกันจะขึ้นอยู่กับการเซตขา AUDIO และขา C เพื่อเลือกสัญญาณว่าต้องการให้สัญญาณเอาต์พุตที่ออกมามีรูปแบบใด ซึ่งรูปของสัญญาณที่ได้จากตัวถอดรหัสสัญญาณเอาต์พุตที่ได้นี้ จะต้องเซตค่าให้ตรงกับ ตัวแปลงสัญญาณดิจิตอลเป็นแอนะลอก (DAC : Digital to Analog converter) ที่ นำมาต่อ เพราะถ้าเซตค่าไม่ตรงกับตัว DAC จะทำให้การแปลงสัญญาณดิจิตอลเป็นแอนะลอกนั้นไม่สามารถทำได้

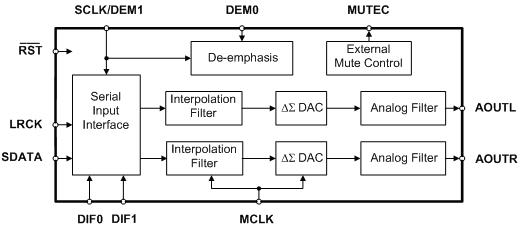

การแปลงสัญญาณดิจิตอลเป็นแอนะลอกโดยไอซี CS4340

วงจรแปลงสัญญาณดิจิตอลเป็นแอนะลอกนั้นมีหลายรูปแบบซึ่งคุณภาพสัญญาณเสียง ที่ได้จะดีหรือไม่นั้นก็ขึ้นอยู่กับวงจรนี้ด้วยในการออกแบบวงจรนี้จะใช้ไอซี เบอร์ CS4340 เป็นไอซีที่สามารถแปลงสัญญาณดิจิตอลเป็นแอนะลอกได้ 16 – 24 บิต ใช้ไฟเลี้ยงได้ตั้งแต่ +3V ถึง +5V สามารถรับสัญญาณดิจิตอลที่เข้ามาทางอินพุตได้ 4 รูปแบบ และให้สัญญาณแอนะลอกออกทางเอาต์พุตได้ทั้งซ้ายและขวา ซึ่งภายในตัวไอซีประกอบด้วย ส่วนของ อินเตอร์โปเลชั่น, ตัวแปลงสัญญาณดิจิตอลเป็นแอนะลอกแบบซิกมา-เดลต้า และ วงจรฟิลเตอร์ รายละเอียดในแต่ละส่วนได้แสดงดังรูปต่อไปนี้

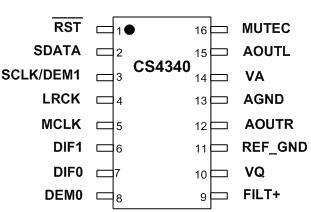

รูปที่ 6 ตำแหน่งขาของ CS4340

รูปที่ 6 ตำแหน่งขาของ CS4340

รูปที่ 7 บล็อกไดอะแกรมภายในตัวไอซี CS4340

ตารางที่ 5 ขาสัญญาณของ ไอซี CS4340

ส่วนภาคจ่ายไฟ ภาคPhase Locked Loop และรีเซ็ต

ขา

|

ชื่อขา

|

รายละเอียดขา

|

14

|

VA

(Analog Power Supply)

|

ขาไฟเลี้ยงบวกของ ภาคแอนะลอกโดยปกติใช้ 3.3 หรือ 5 โวลต์ |

13

|

AGND

(Analog Ground)

|

เป็นขากราวด์สำหรับวงจรแอนะลอกของไอซี CS4340 |

9

|

FILT+

(Positive Voltage Reference)

|

เป็นขาที่ใช้สร้างความถี่ในการล็อกสัญญาณอินพุต |

10

|

VQ

(Quiescent Voltage)

|

เป็นขาที่ใช้เป็นแรงดันอ้างอิงในการต่อฟิลเตอร์ |

11

|

RET_GND(Reference Ground)

|

เป็นจุดกราวด์อ้างอิงให้กับวงจรฟิลเตอร์และวงจรสุ่ม (Sampling)ใน CS4340 |

1

|

RST

(Reset) |

เมื่อขา RST มีสภาวะเป็น Low จะเป็นการรีเซ็ตของตัวไอซี CS4340 และเมื่อขา RST มีสภาวะเป็น High ไอซี CS4340 จะทำงานตามปกติ |

2

|

SDATA

(Serial Audio Data)

|

ขาที่รับข้อมูลเสียงแบบอนุกรมแบบ Two’s Complement จากวงจรถอดรหัสสัญญาณ CS8416 |

3

|

SCLK

(Serial Clock)

|

ขาที่รับ สัญญาณนาฬิกา ของข้อมูลเสียงแบบอนุกรมจากวงจรถอดรหัสสัญญาณCS8416 |

4

|

LRCK(Left Right Clock)

|

เป็นขาที่รับสัญญาณนาฬิกาที่เป็นตัวชี้ว่าเป็นสัญญาณเสียงเสียงทางด้านซ้ายหรือสัญญาณเสียงทางด้านขวาจากไอซี CS8416 |

5

|

MCLK

(Master Clock)

|

เป็นขาที่รับ สัญญาณนาฬิกา ที่เอาไปใช้กับวงจรดิจิตอล อินเตอร์โพเลนชั่น และซิกม่า-เดลต้า ที่อยู่ภายในไอซี CS4340 |

ส่วนภาคควบคุมและภาคแอนะลอกเอาต์พุต

7,6

|

DIF0 และ DIF1

|

เป็นขาที่ใช้เลือกรูปแบบของสัญญาณเสียงดิจิตอลแบบอนุกรม (Audio Serial Data) |

8,3

|

DEM0 และขา DEM1

(De-emphasis)

|

เป็นขาที่ใช้เซตค่าความถี่ของขา SCLK ที่เป็นสัญญาณภายใน ถ้ารับสัญญาณ SCLK จากภายนอกจะใช้ขา DEM0 เป็นตัวเลือก |

15,12

|

AOUTL และ AOUTR เอาต์พุต

|

สัญญาณเสียงแอนะลอกซ้ายขวา |

16

|

MUTEC

(Mute Control) |

เป็นขาเอาต์พุต จาก CS4340 ที่ส่งออกไปควบคุมวงจรตัดเสียงเมื่อไม่มีสัญญาณ สัญญาณเสียงดิจิตอลแบบอนุกรม (Audio Serial Data) เข้ามาที่ CS4340 |

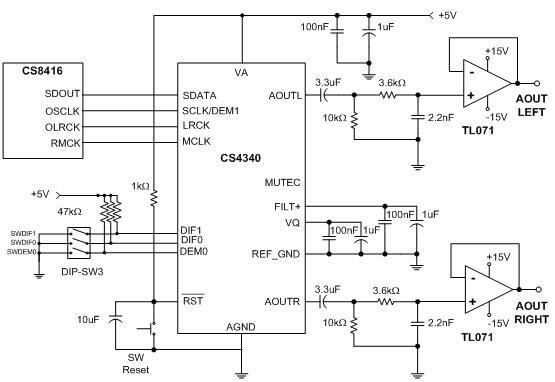

การออกแบบวงจรแปลงสัญญาณดิจิตอลเป็นแอนะลอกโดยไอซี CS4340

จากรูปเป็นการออกแบบวงจรแปลงสัญญาณดิจิตอลเป็นแอนะลอกโดยใช้ไอซี CS4340 ซึ่งจะใช้ไฟเลี้ยงวงจร +5V ที่ขา VA รับสัญญาณดิจิตอลจาก CS8416 เข้ามา 4 สัญญาณด้วยกัน คือ SDOUT,OSCLK,OLRCK และ RMCK มาเข้าที่ขา SDATA,SCLK,LRCK และ MCLK ของ CS4340 ตามลำดับดังรูปที่ 3.15 โดยมีขา FILT+ เป็นขาที่ใช้สร้างความถี่ในการล็อกสัญญาณของอินพุต และ VQ เป็นขาที่ใช้เป็นแรงดันอ้างอิงในการต่อฟิลเตอร์ โดยจะได้สัญญาณแอนะลอกทั้งซ้ายและขวา ออกทางเอาต์พุตที่ขา AOUTL และ AOUTR ตามลำดับ และจะนำสัญญาณที่ได้นี้ไปผ่านวงจรกรองความถี่แถบผ่าน (Band Pass Filter) กำหนดให้มีความถี่ตัดที่ 5Hz และ 20kHz จากนั้นจึงจะไปเข้าไลน์-สเตจ (Line Stage) ในที่นี้ออกแบบเป็น ออปแอมป์ มีอัตราขยายเท่ากับ 1 ต่อเป็นบัฟเฟอร์ให้กับวงจรเป็นส่วนสุดท้าย

รูปที่ 8 การออกแบบวงจรแปลงสัญญาณดิจิตอลเป็นแอนะลอกโดยไอซี CS4340

- I2S up to 24 bit data

- Left Justified up to 24 bit data

- Right Justified to 24 bit data

- Right Justified to 16 bit data

ตารางที่ 6 การเซตโหมดการรับสัญญาณอินพุต

| DIF1 | DIF0 | DESCRIPTION |

0

|

0

|

I2S up to 24 bit data |

0

|

1

|

Left Justified up to 24 bit data |

1

|

0

|

Right Justified to 24 bit data |

1

|

1

|

Right Justified to 16 bit data |

ตารางที่ 7 การเลือกใช้ De-Emphassis ความถี่ที่ใช้ในการสุ่ม

DEM1

|

DEM0

|

DESCRIPTION

|

0

|

0

|

Disabled

|

0

|

1

|

44.1kHz

|

1

|

0

|

48 kHz

|

1

|

1

|

32 kHz

|

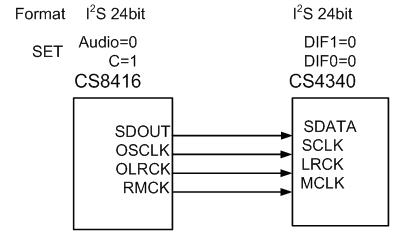

รูปที่ 9.1 การต่อวงจรCS8416เข้ากับ CS4340

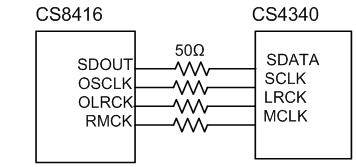

รูปที่ 9.2 การต่อความต้านทานระหว่างวงจรCS8416 กับ CS4340

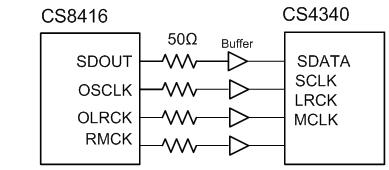

รูปที่ 9.3 การต่อความต้านทานและบัฟเฟอร์ระหว่างวงจรCS8416เข้ากับ CS4340

รูปที่ 9.2 เป็นเทคนิคในการต่อโดยการเพิ่มตัวต้านทานเข้าไประหว่างวงจรทั้งสองเพื่อลด สัญญาณลดกวนจากคลื่นสนามไฟฟ้าแม่เหล็กต่างๆ ส่วนรูปที่ 9.3 นอกจากจะมีตัวต้านทานแล้ว ถ้าต้องการใช้ต่อกับ DAC หลายตัวก็ควรจะเพิ่ม บัฟเฟอร์เข้ามาด้วย โดยบัฟเฟอร์ที่จะใช้อาจจะใช้ 74HC04 , 74HC125 , 74HC245 ก็ได้

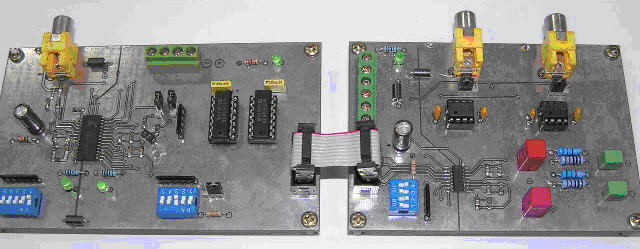

รูปที่ 10 บอร์ดวงจร CS8416 กับ CS4340 ที่ประกอบเสร็จแล้ว

รูปที่ 10 บอร์ดวงจร CS8416 กับ CS4340 ที่ประกอบเสร็จแล้วสำหรับการต่อวงจร CS8416 กับ วงจรดีทูเอของบริษัทอื่นนั้นก็มีรูปแบบการต่อที่เหมือนกันแต่ต่างกันที่ตัว ดีทูเอของแต่ละบริษัทจะมีวงจรดีทูเอ, วงจร ฟิวเตอร์และวงจรแอนะลอก ที่การต่อใช้งานได้ยากง่ายต่างกันเท่านั้นในครั้งต่อไปอาจจะลองแนะนำการใช้ วงจรดีทูเอของ Burr-Brown ซึ่งถือว่าเป็นดีทูเอ ออดิโอที่มีคุณภาพอย่างสูงแต่ต่อ ยากกว่าของ Crystal รวมทั้งรายละเอียดของสัญาณญ SPDIF ที่มากขึ้นด้วย

ไม่มีความคิดเห็น:

แสดงความคิดเห็น